The second MEMOCODE Hardware/Software Co-Design Contest, organized by the MEMOCODE Conference technical and steering committees, has completed.

- The details of the contest assignment are still available.

- The results page lists the finishing teams, the ranking, and the awards.

- Several of finishing teams have agreed to share their

submissions!

Their designs are available on the results page.

Similar to last years contest, a design challenge will be posted on the start date of the contest. The design teams have 30 days to produce a working implementation employing any HW and SW design methodology and targeting any FPGA development platform of the contestants' choice.

Contest starts on February 8, 2008, 12:01AM ET.

Contest ends on March 9, 2008, 11:59PM ET.

Awards will be handed out in two regular categories and one special category. A design can only win in a single regular category. However, all designs can win in the special category. If a design would be entitled to win across multiple regular categories, the judges will make the final decision on the awarded regular category.

The judging panel will evaluate each submission and rank them according to different categories as listed below.

- Regular - The Most Efficient Design is in part judged on a

performance metric that allows normalization across

implementation platforms of different capabilities.

The winner in this category receives a $1000 cash award.

- Regular - The Highest Performance Design is in part judged on

absolute performance delivered.

The winner in this category receives a $1000 cash award.

- Special - Best Figures of Merit Using a High Level

Language is in part judged on the use of a high-level

design language or environment. For example, Bluespec or

GEZEL appearing in the 2007 solutions would both be eligible.

A commercially synthesizable subset of Verilog or VHDL would

not be eligible. If in doubt, please consult the

organizers.

The winner in this category will receive the following special prize sponsored by Xilinx: (a) cash prize of $1000, (b) complete environment including hardware and software with the latest Xilinx technology, (c) an invitation with domestic travel paid for one speaker to come to Xilinx Labs and present the results and rationale for the design.

Awards are sponsored by the following companies and organizations

|

|

|

|

Interested participants should contact the organizers listed below and propose a team. At the start of the contest, the organizers will provide a software-only starter reference solution for the Xilinx XUP development board on these pages. You are not limited to using Xilinx XUP or the EDK tools for the contest (see below).

Before the contest gets underway, participants are highly encouraged to familiarize themselves with the FPGA platform hardware and design tools. Experience has shown that valuable design time gets lost during the contest due to 'learning-curve' issues with tools.

Please visit last year's contest site to see an example of a contest problem.

The 2008 contest will be jointly organized by Krste Asanovic (UCB), James C. Hoe (CMU), and Patrick Schaumont (Virginia Tech). If you are interested in receiving future notifications, please email the organizers at the address below with your contact information (team member names and affiliation).

Contact Email Address: memocontest08@gmail.com

A design challenge will be posted at this website on the start date of the contest (2/8/2008). The design teams have 30 days to produce a working solution. The solution must work correctly to be considered for awards.

You may use any HW and SW design methodology at your disposal. Formal methods are encouraged but not required.

You may use any development platform at your disposal. The platform can include any number of processors and FPGA devices. The processor and/or the FPGA should have access to at least 512 MegaBytes of memory.

The reference platform supported by the contest organizers is the Xilinx XUP development board with 512MB of DRAM. For those of you using XUP, we provide a reference EDK project for the Xilinx XUP board that implements a basic interface library to enable communication between the software running on the 300MHz embedded PowerPC405 and the 100MHz FPGA fabric through the DSOCM interface (150+MB/sec bandwidth). The interface is based on two circular memory FIFOs, one for each direction of data communication between the hardware and the software. You may develop or acquire any other interfacing scheme you prefer.

A subjective element of judging is based on the elegance the solutions as determined by the panel of judges.

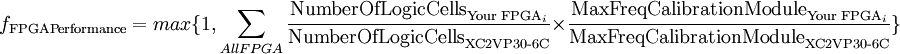

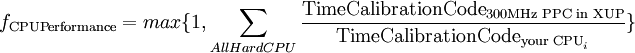

In addition, a design is judged both for absolute performance and normalized performance (efficiency) in the objective portion of the judging. Separate awards are given in the two categories.

The absolute performance is determined by execution time

(wall-clock). The normalized performance is determined by

normalizing the execution time for platform differences. The

normalized execution time will be computed as

The normalization factor for the XUP platform (with a -6 XC2VP30) is 1. If you use a platform different from XUP, you will have to obtain the normalization factor for your platform as specified below under Platform Calibration.

For each category of performance competition, the entries are ranked overall by the value (Rank_performance + Rank_elegance). In the case of a tie, Rank_performance is the tie-breaker. Top two finishers in each category will have the opportunity to present their design and design methodology in MEMOCODE-08's technical program. All entrants are invited to submit a poster for Memocode's Poster Session. Travel assistance will be available to the invited top finishers. We will offer a cash prize for the winning design.

The winning designs must work correctly. We rely on the honor systems for initially reporting the performance data. In the case you should be among the top finishers, we will arrange verification of the correctness of your design and the performance data.

See also the Code Calibration Page

The contest awards both absolute performance as well as normalized performance. If you use an XUP board (with a -6 XC2VP30) to enter the contest, your performance normalization factor is 1. If you use a more "capable" platform, your normalization factor will be greater than 1. If you use a less capable platform, however, your normalization factor cannot go below 1.

If you use a platform difference from XUP, you are

responsible to obtain the normalization factor for your

platform as follows. The normalization factor is given by the

following formulas.

with

and

For the purpose of calibration, we treat a Xilinx Logic Cell and an Altera Logic Element as equivalent (comprising 1 LUT, 1 flop, and carry logic). The following constants must be used in these formulas.

|

30,816 Logic Cells (based on Vendor-published Xilinx LC or Altera LE Count) |

|

67.9 MHz (ISE 9.1, post place-and-route) |

|

0.1573 sec |

Please consult the Calibration

Code Page to download the source code of the hardware and

software modules that you must use to measure  and

and  . You will need to include all FPGA as well as all

hard CPU in your system to determine the overall normalization

factor.

. You will need to include all FPGA as well as all

hard CPU in your system to determine the overall normalization

factor.

If you feel your platform is not fairly calibrated this way, please contact the contest organizers for a case-by-case determination. In any case, if an entry is based on an extraordinary platform, the judging panel reserves the right to determine a fair normalization on a case-by-case basis.

Eligibility and Entry Instructions

This contest is open to industry and academic institutions (faculty and/or students). A team may include both industry and academic members. There is no limit on the size of a team. There is no limit on the number of teams per institution. Each person can participate in only one team.

To enter, return to this website on 2/8/2008, to register for the design problem and the reference implementation. We will respond by sending you the SW-only reference design (portable C) and the XUP HW/SW interface design (C and Verilog in an EDK project). There are no obligations associated with requesting the reference designs.

Before 3/9/2008, submit your solution and a brief documentation describing

- your FPGA platform

- your design methodology

- the organization of your design and its theory of operation

- a brief analysis of its performance (e.g., where are time spent and where are the bottlenecks).

- Documentation in the form of PowerPoint slides is perfectly acceptable.