# **Industry Pulse:**

Trends in Functional Verification

Harry Foster Chief Scientist Verification Design Verification Technology

MemoCODE 2013

#### **Extrapolating From Current Conditions Disregards Future Innovation**

"In 1910, in the early history telephony, a Bell telephone statistician projected a massive ramp-up in switchboard operator jobs as telephone use grew, until "every woman in America" would be required."

Source: Future Savvy: Identifying trends to Make Better Decisions, Manage Uncertainty, and Profit From Change Adam Gordon, 2008

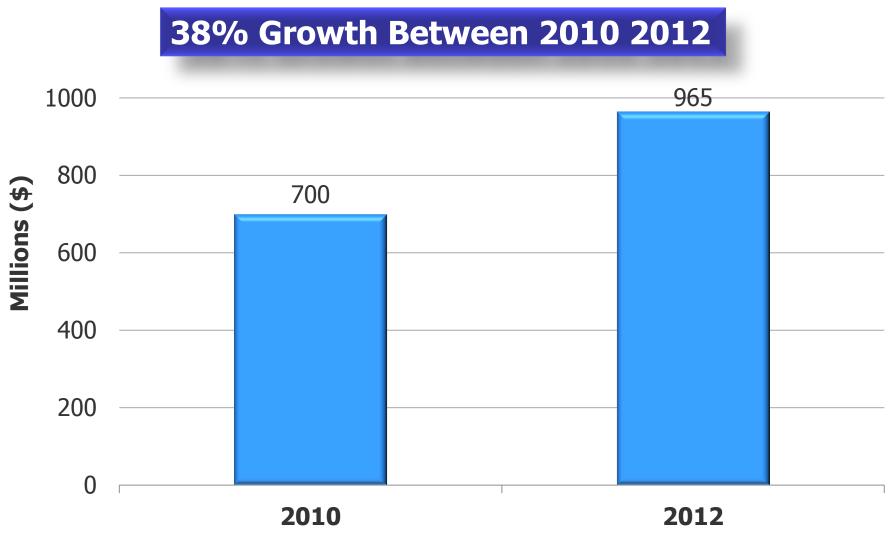

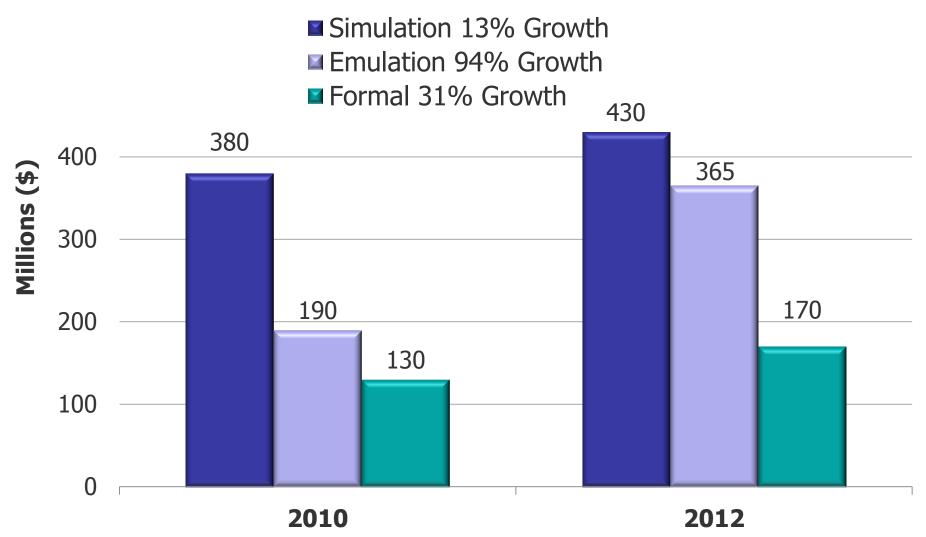

#### **Functional Verification Market** According to EDAC

EDAC: Market Statistics Service 2007 Annual Summary Report

© 2013 Mentor Graphics Corp. Company Confidential **www.mentor.com**

#### **Functional Verification Market** According to EDAC

EDAC: Market Statistics Service 2007 Annual Summary Report

#### **2012 Wilson Research Group**

Functional Verification Study

- Conducted by Wilson Research Group

- Commissioned by Mentor Graphics

- Format followed 2002, 2004 Collett studies for trend analysis, as well as the 2007 FarWest Research Study

- Worldwide study

- Overall confidence of 95% plus/minus 4.05%

- This was a blind study!

- To eliminate any bias in the results

- This was a balanced study!

- No single vendor dominated responses

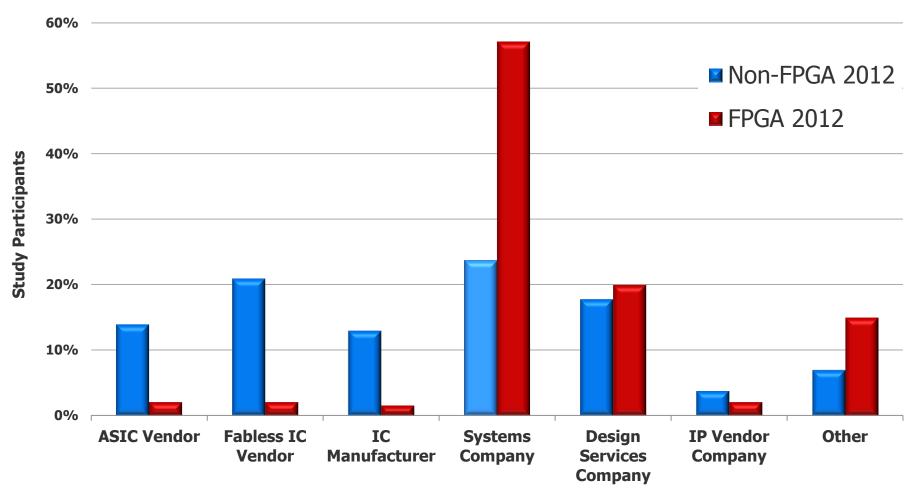

#### **Who Participated In The Survey**

Participant's market segment

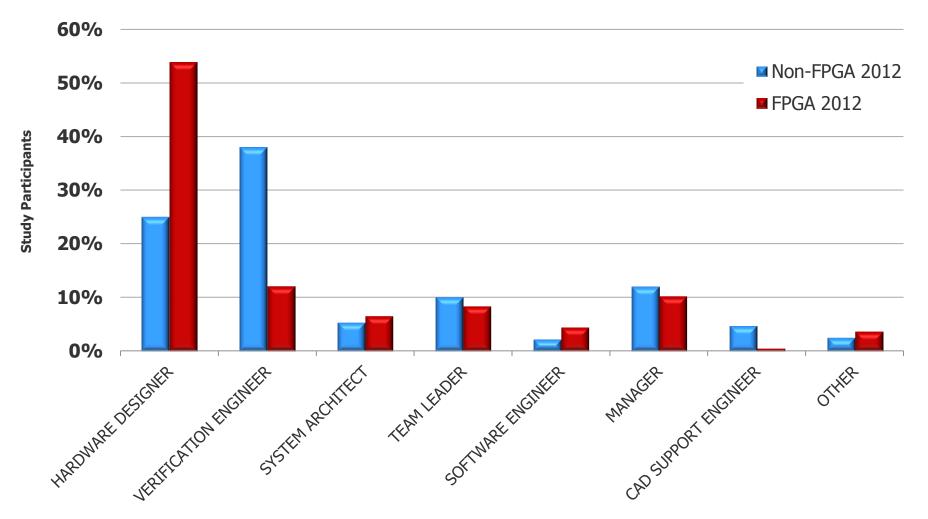

#### **Who Participated In The Survey**

Participant's job title

#### **Overview**

- Beyond Theory

- Beyond Standards

- Beyond the Status Quo

Beyond Theory in Terms of Rising Complexity

## **BEYOND THEORY**

# In theory there is no difference between theory and practice, but in practice there is.

#### Theory: Everything is clear, but nothing works.

#### Practice: Everything works, but nothing is clear.

#### The problem is sometimes theory meets practice: Nothing works and nothing is clear.

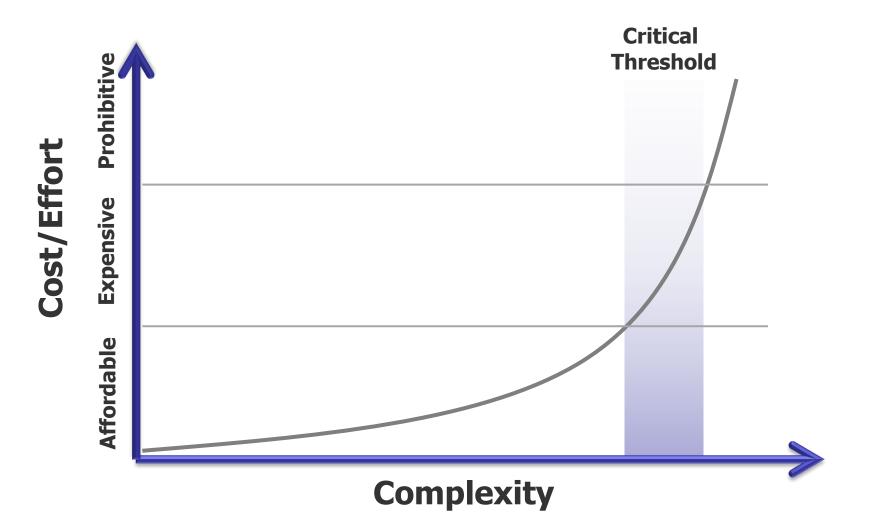

#### **Beyond Theory in Terms of Rising Complexity**

- What does this really mean?

- What makes things complex?

- How do we measure complexity?

## What Makes Something Complex?

- System consisting of many interconnected parts

- Examining the individual parts tells you nothing about the system

- Complex does not necessarily mean complicated

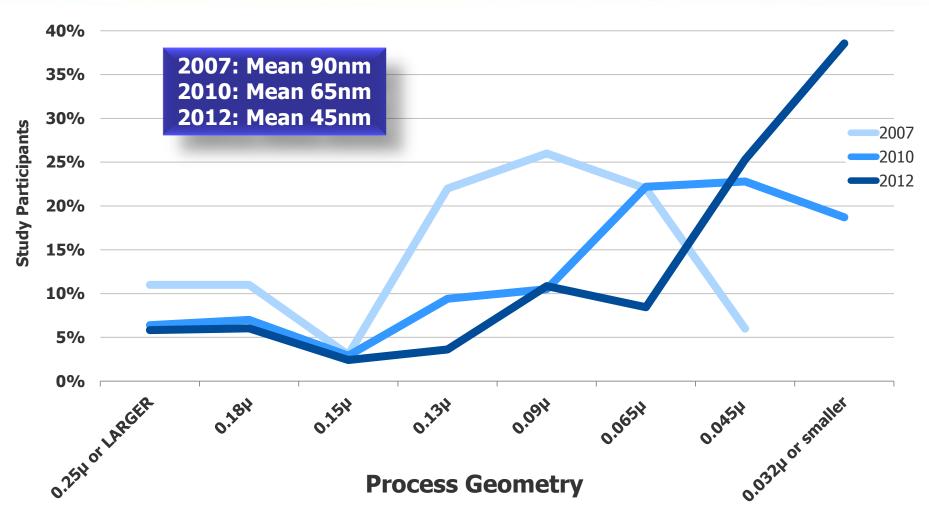

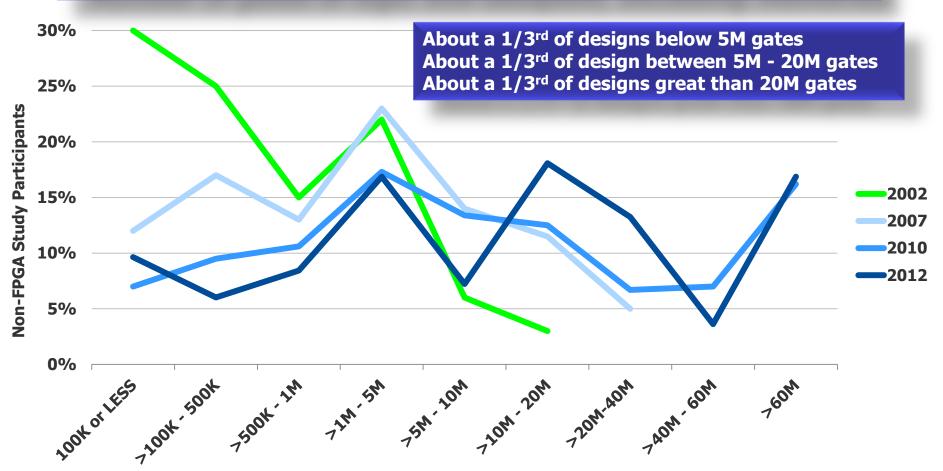

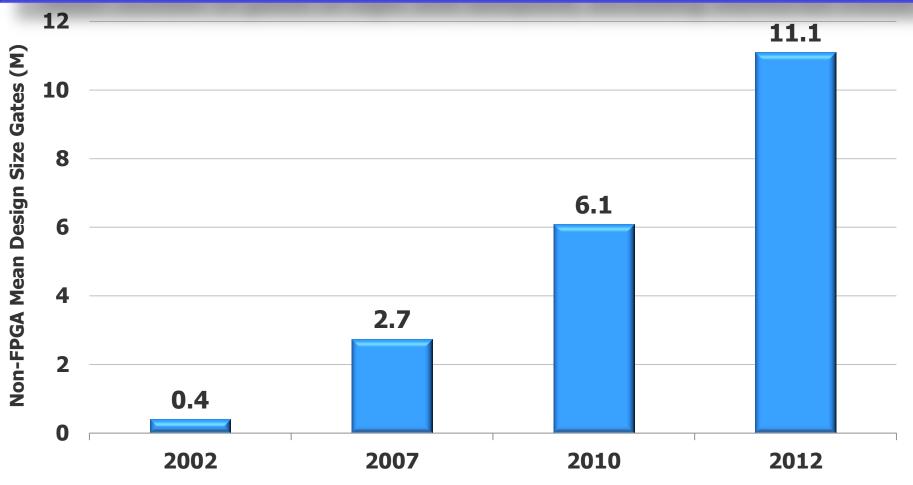

Number of gates of logic and datapath, excluding memories

Mean number of gates of logic and datapath, excluding memories trends

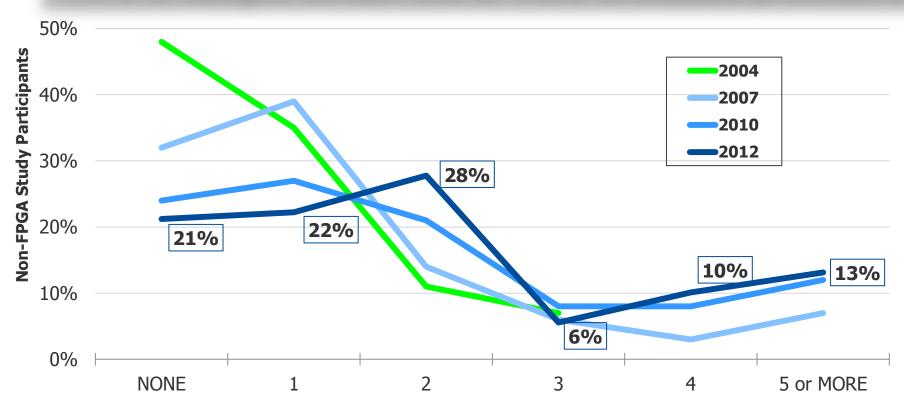

Number of Embedded Processors for Non-FPGA Designs

Source: Wilson Research Group and Mentor Graphics, 2012 Functional Verification Study

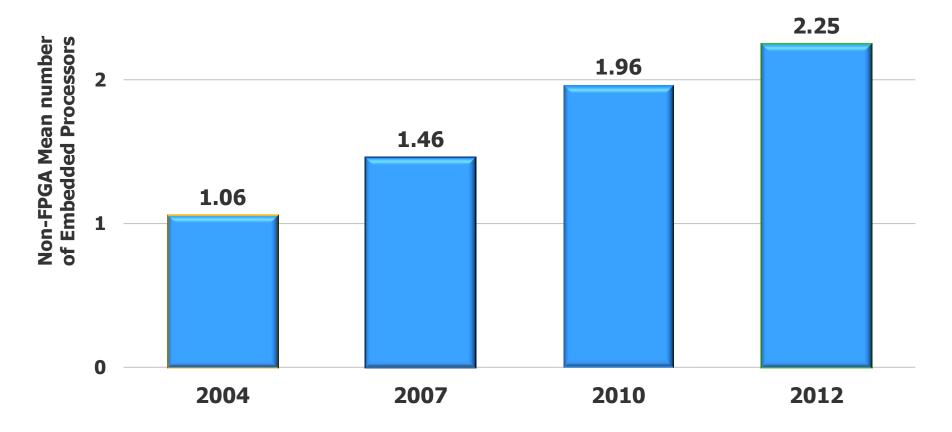

Mean number of embedded processors continues to rise

Source: Wilson Research Group and Mentor Graphics, 2012 Functional Verification Study

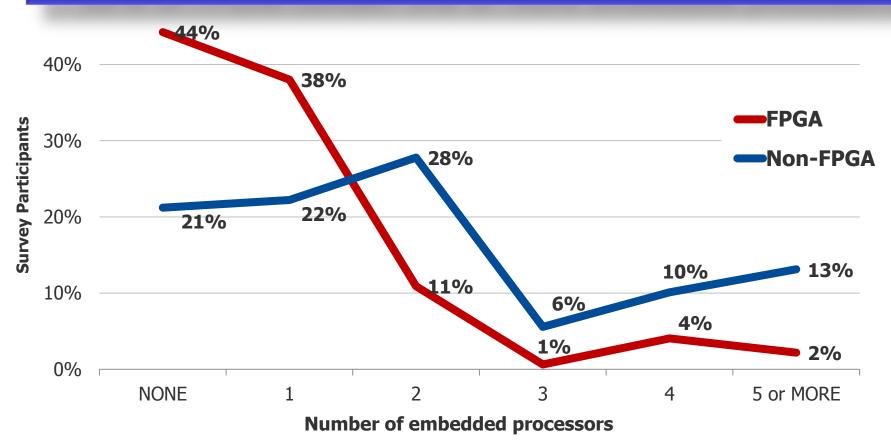

## **FPGAs are Getting Complex Too!**

56% of FPGAs contain one or more embedded processors

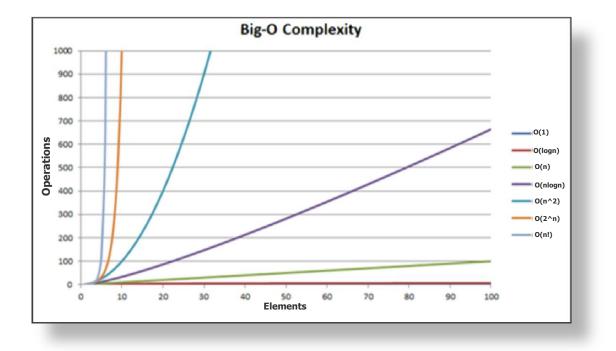

## How do we measure complexity?

Computational complexity theory used in computer science

There are no generally accepted metrics!

## Is bug density a good proxy?

-Ted Scardamalia, internal IBM study

© 2013 Mentor Graphics Corp. Company Confidential **www.mentor.com**

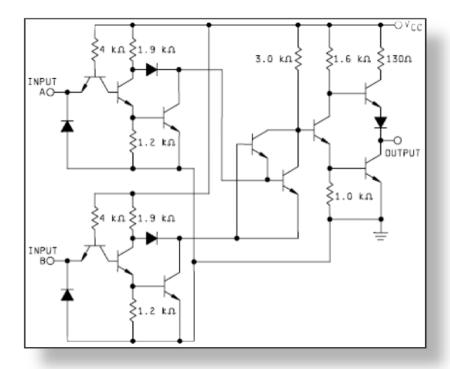

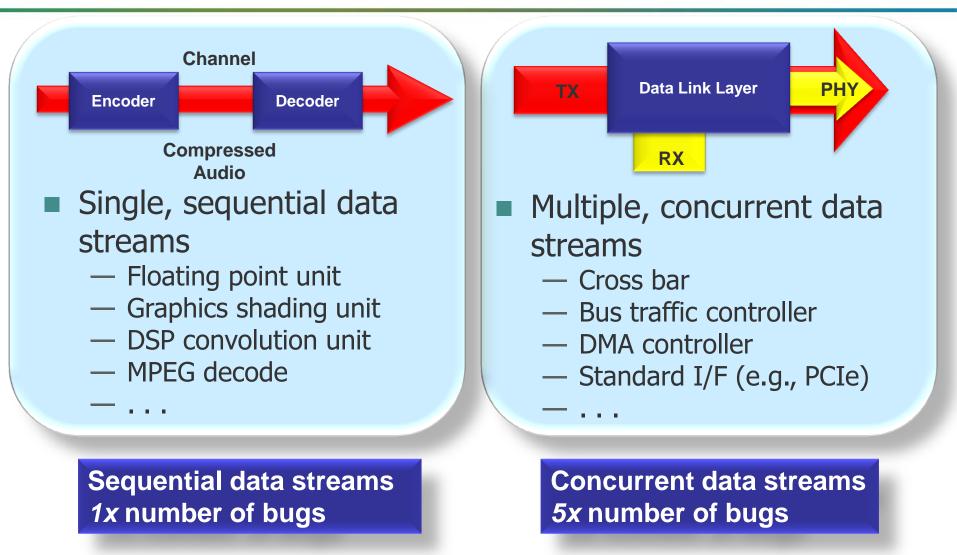

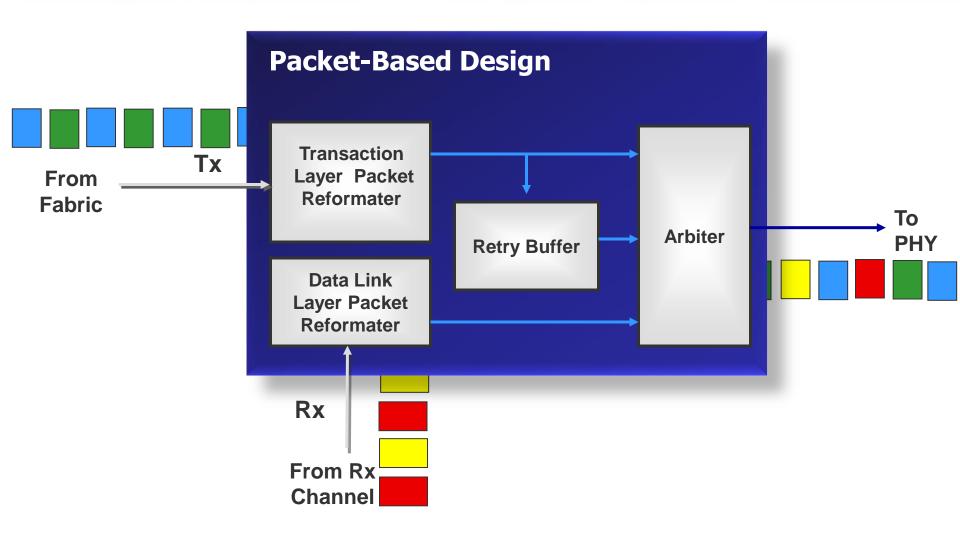

## **Concurrency is Complicated to Verify**

## Maybe effort is a good proxy?

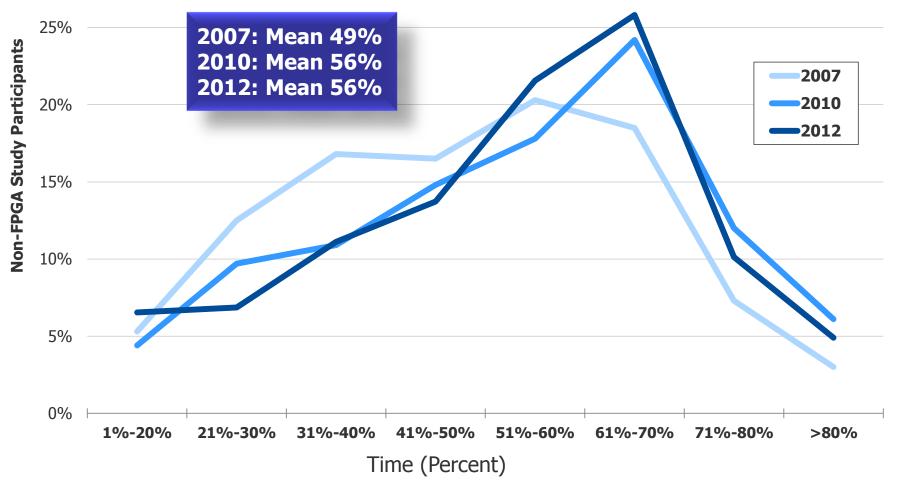

#### **Verification Consumes Majority of Project Time**

#### **Total Project Time Spent in Verification**

Wilson Research Group and Mentor Graphics, 2012 Functional Verification Study

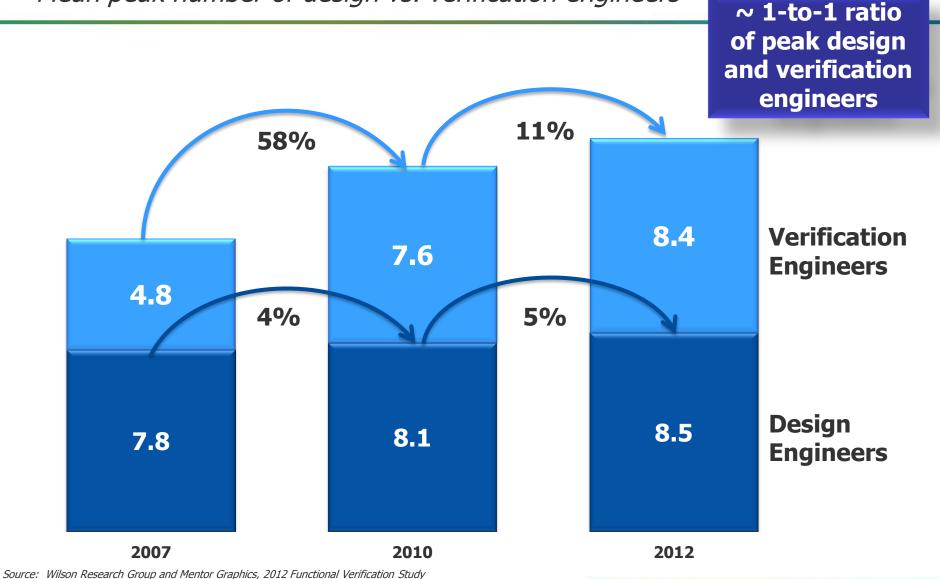

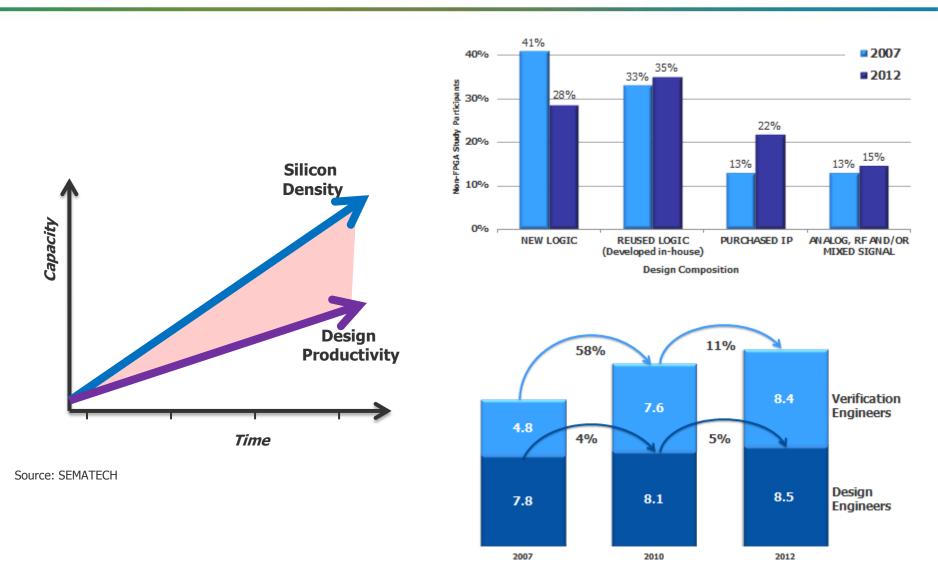

#### **More and More Verification Engineers**

Mean peak number of design vs. verification engineers

#### **Where Verification Engineers Spend Their Time**

# More time spent in debug than any other task!

- Test Planning

- Testbench Development

- Creating and Running Test

- Debug

- Other

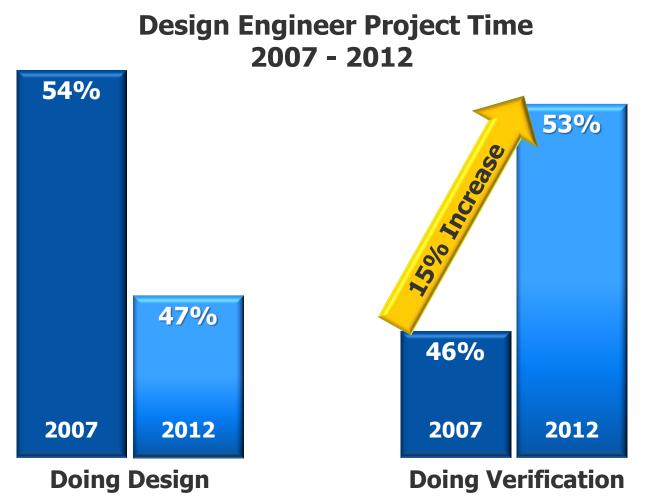

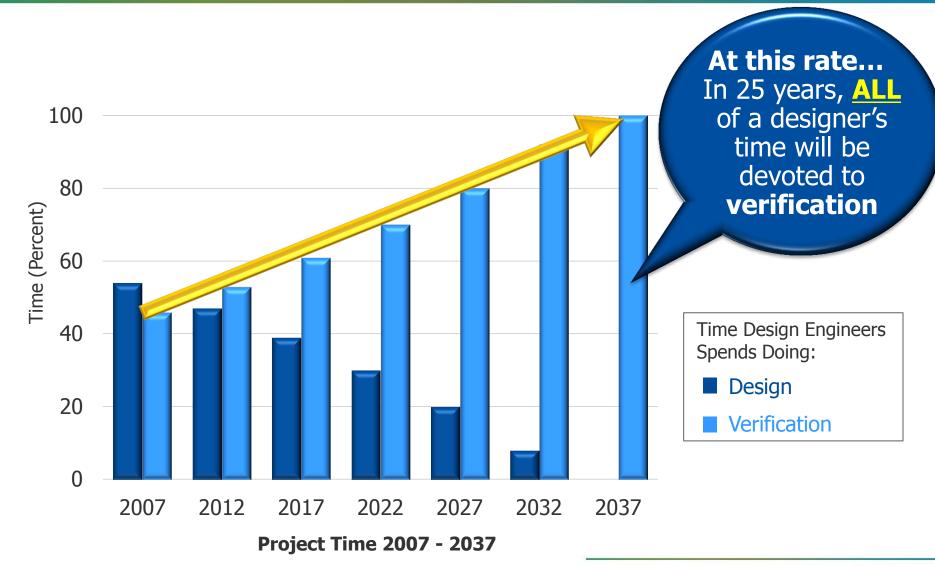

#### **Designers Doing More and More Verification**

Source: Wilson Research Group and Mentor Graphics, 2012 Functional Verification Study

#### **Time Designers Spends in Design vs. Verification**

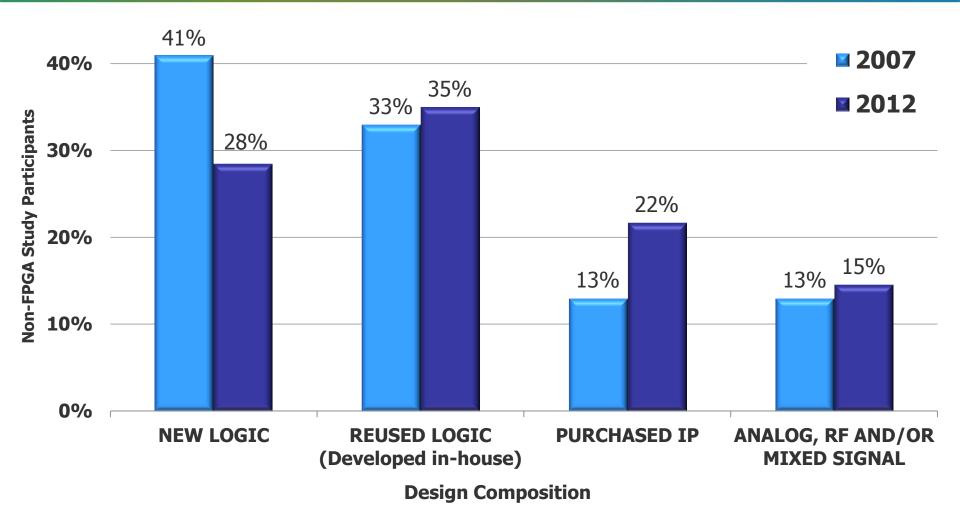

#### **Design Reuse Trends**

Source: Wilson Research Group and Mentor Graphics.

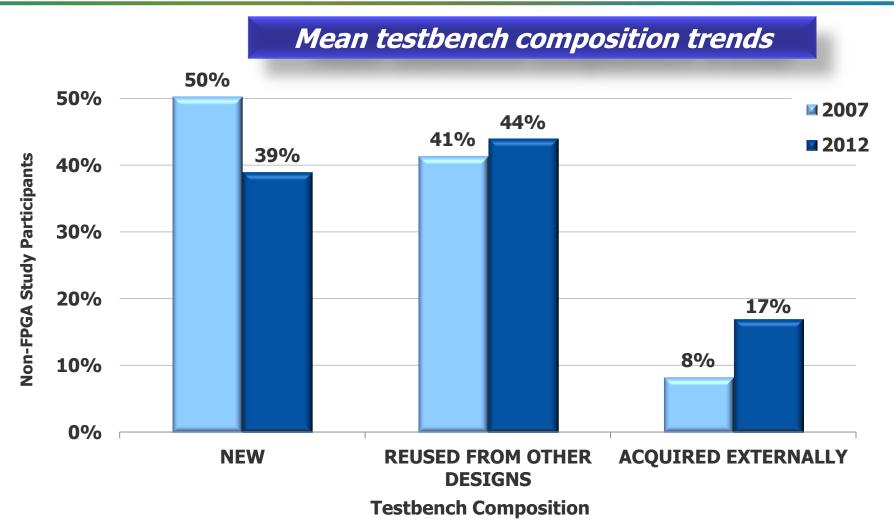

## **Verification Reuse**

### With All This Effort, How are We Doing?

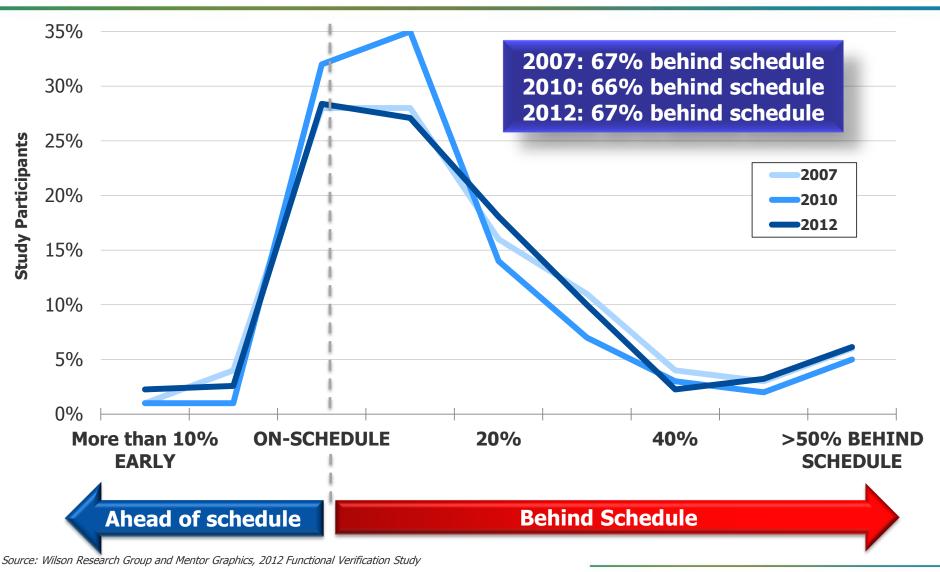

## **Project's Schedule Completion Trends**

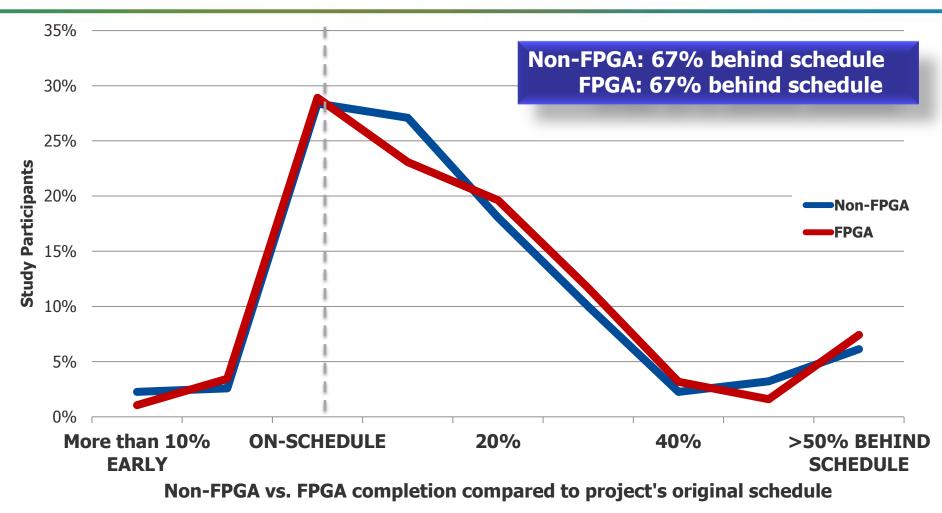

## **FPGA vs. Non-FPGA Completion Trends**

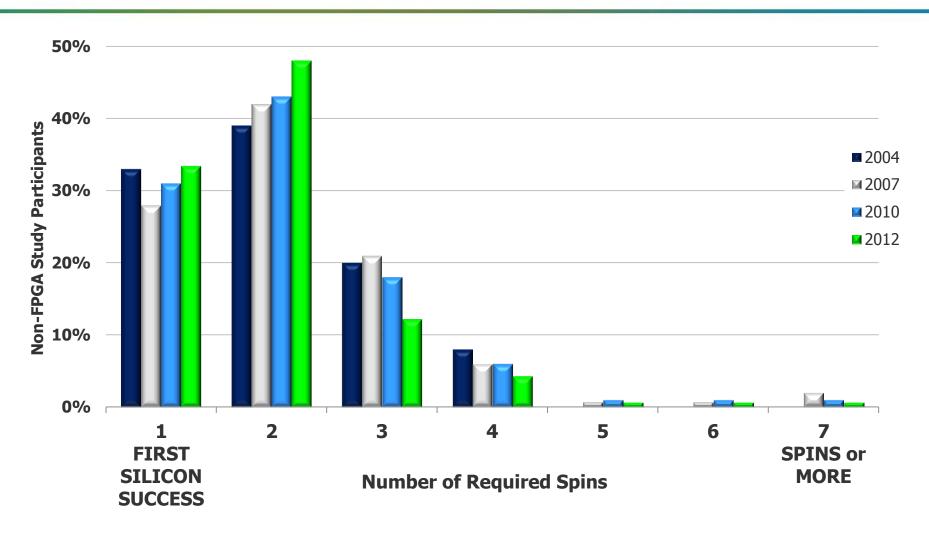

## **Required Number of Spins**

# **Types of Flaws**

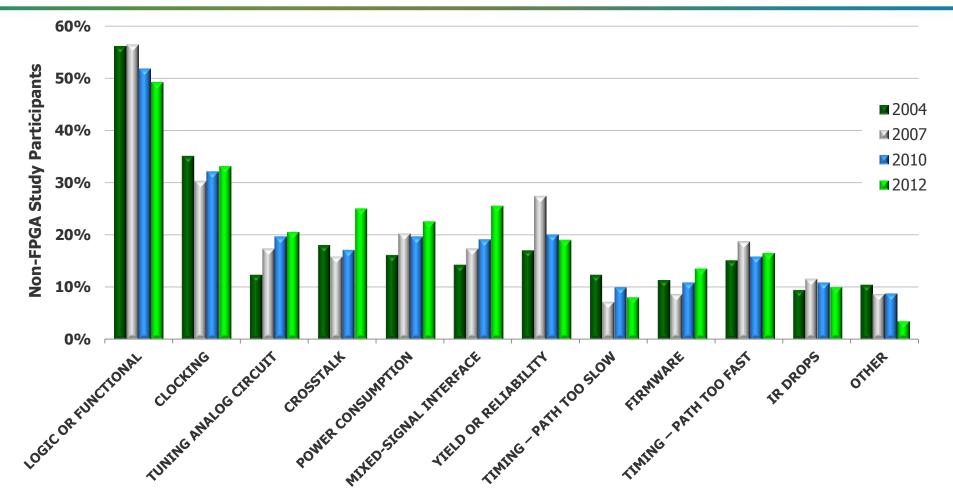

### **Trends in Types of Flaws Resulting in Respins**

Wilson Research Group and Mentor Graphics, 2012 Functional Verification Study, Used with permission

\* Multiple answers possible

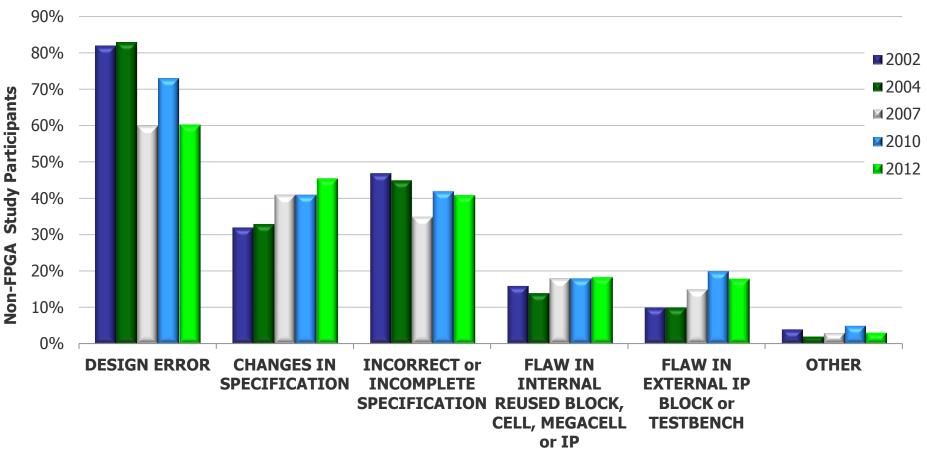

# **Root Cause of Functional Flaws**

### **Root Cause of Functional Flaws**

Wilson Research Group and Mentor Graphics, 2012 Functional Verification Study, Used with permission

\* Multiple answers possible

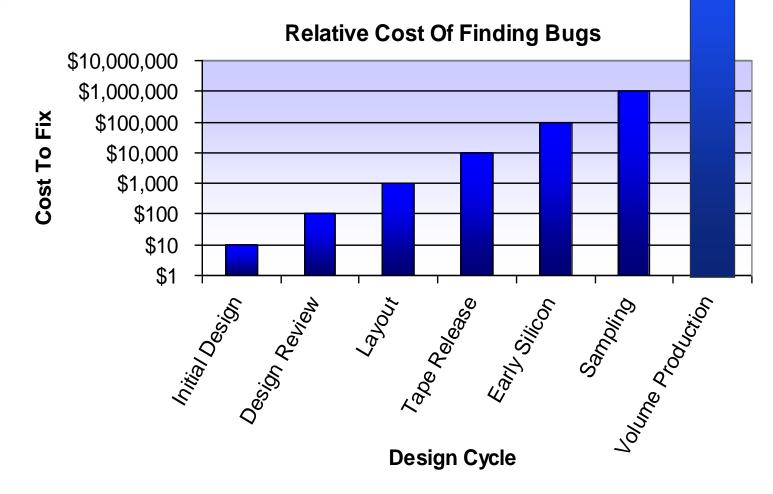

# **Cost of Find Functional Flaws**

Silicon Debug, Doug Josephson and Bob Gottlieb, (Paul Ryan) D. Gizopoulos (ed.), Advances in Electronic Testing: Challenges and Methodologies, Springer, 2006 Beyond arguing over who won the standards war

# **BEYOND STANDARDS**

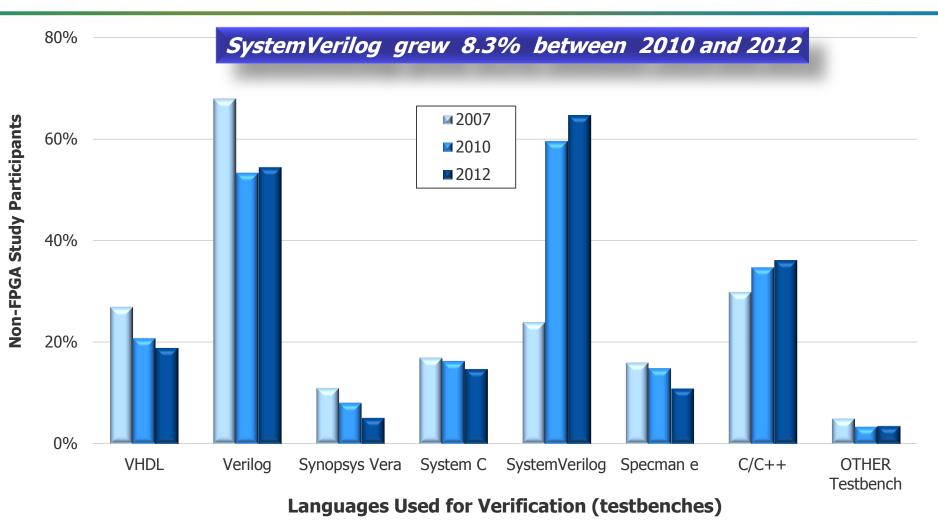

# **Standardization of Languages**

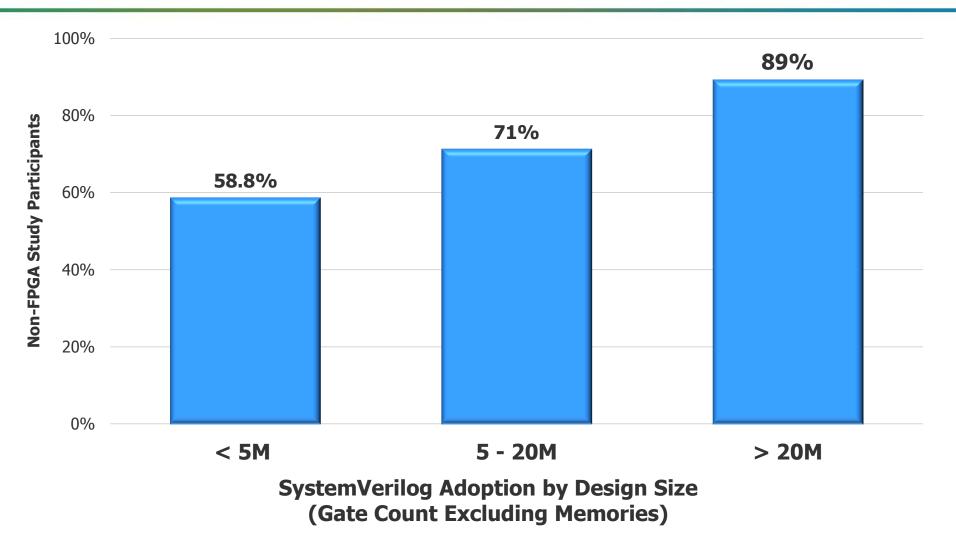

# **SystemVerilog Adoption by Design Size**

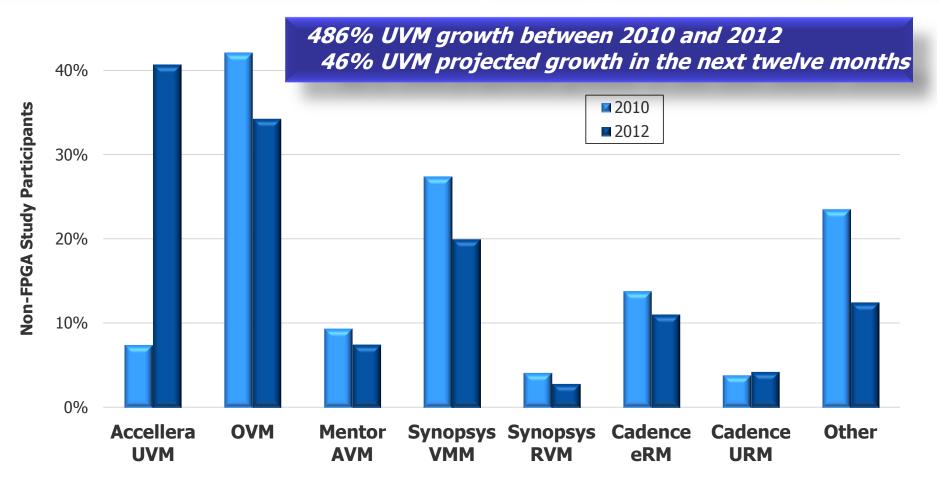

# **Standardization in Base Class Libraries**

#### **Testbench Methodologies and Base-Class Libraries**

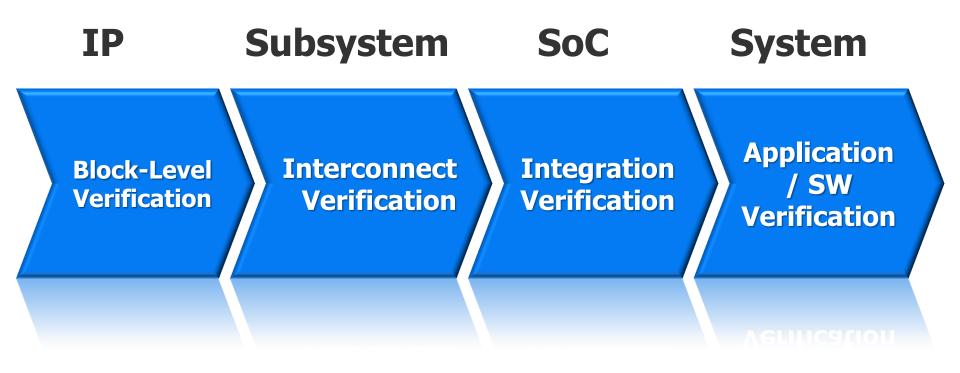

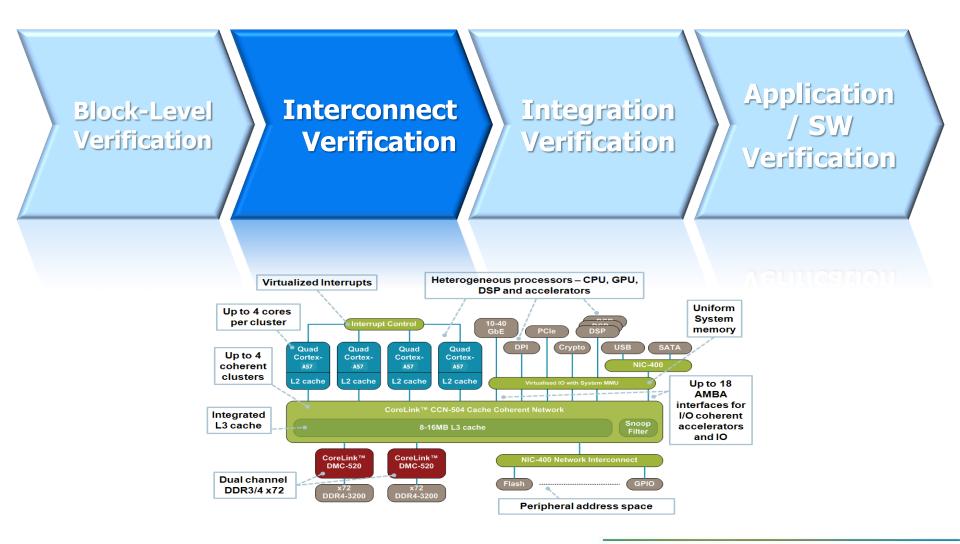

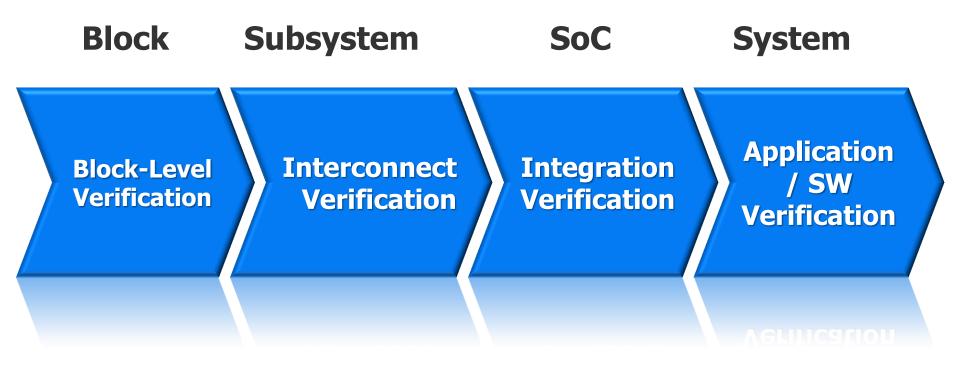

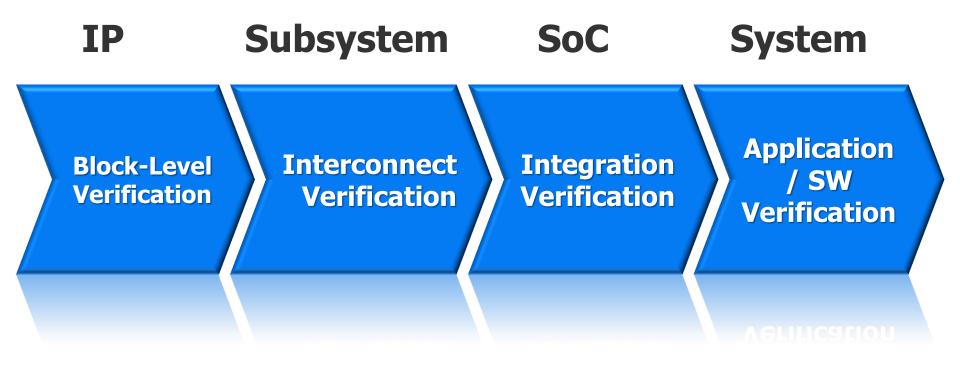

## **Standardization of the SoC Verification Process**

Ten years ago, IC/ASIC verification was partitioned into two main steps:

### **Standardization of the SoC Verification Process**

Emerging from *ad hoc* to systematic processes

Beyond surviving by maintaining the status quo

# **BEYOND THE STATUS QUO**

# **The Verification Paradox**

A good verification process lets you get the most out of best-in-class verification tools

Source: Cisco Momentum Research Group

### **Standardization of the SoC Verification Process**

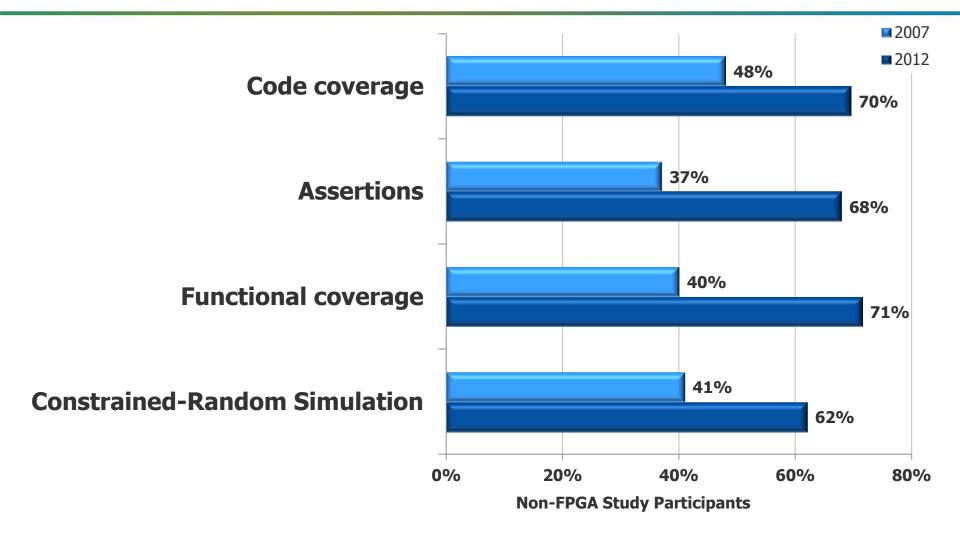

## **Use of Advanced Verification Techniques**

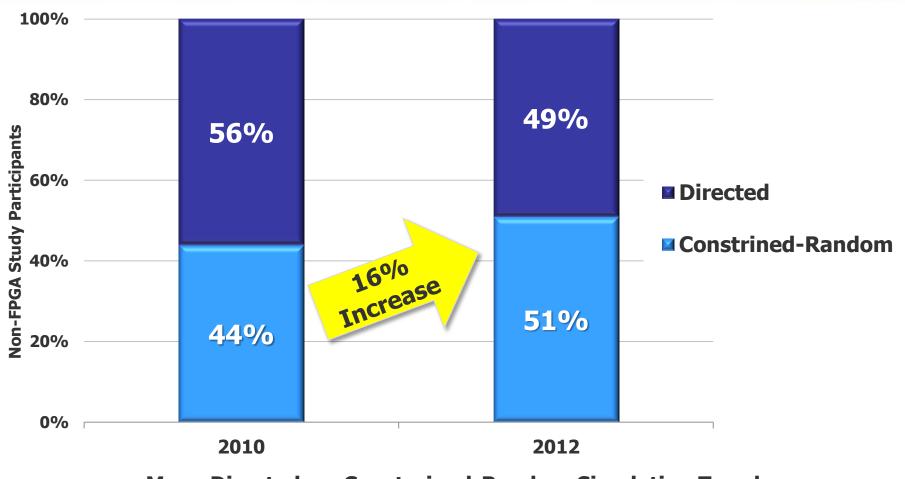

## **Directed vs Constrained-Random Simulation**

### Mean Directed vs. Constrained-Random Simulation Trends

Wilson Research Group and Mentor Graphics, 2012 Functional Verification Study, Used with permission

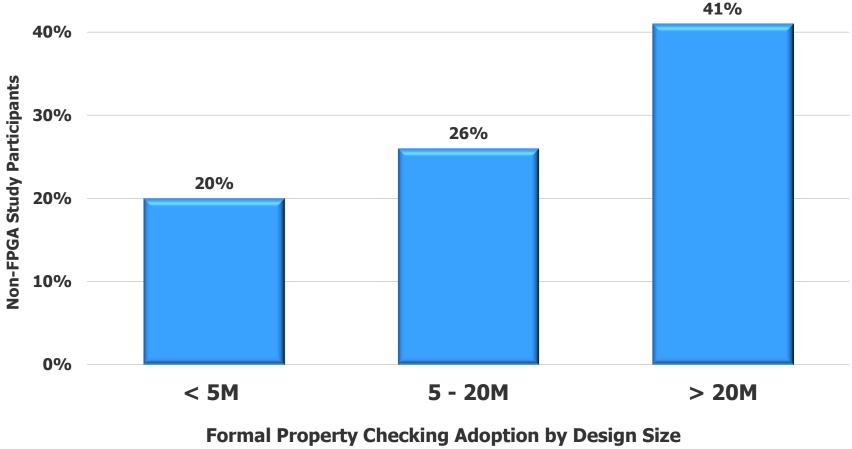

# Larger Designs Use More Formal

(Gate Count Excluding Memories)

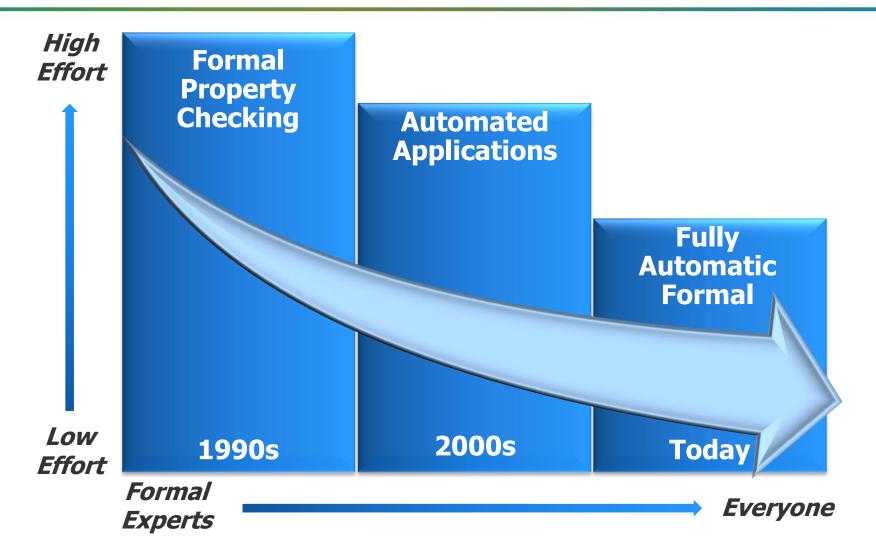

## **The Evolution of Formal Technology**

### **Standardization of the SoC Verification Process**

## **Standardization of the SoC Verification Process**

- IP Blocks connectivity

- Access all memories

- Access all registers, such as control

- Configurations work

- Functional scenarios and use-cases

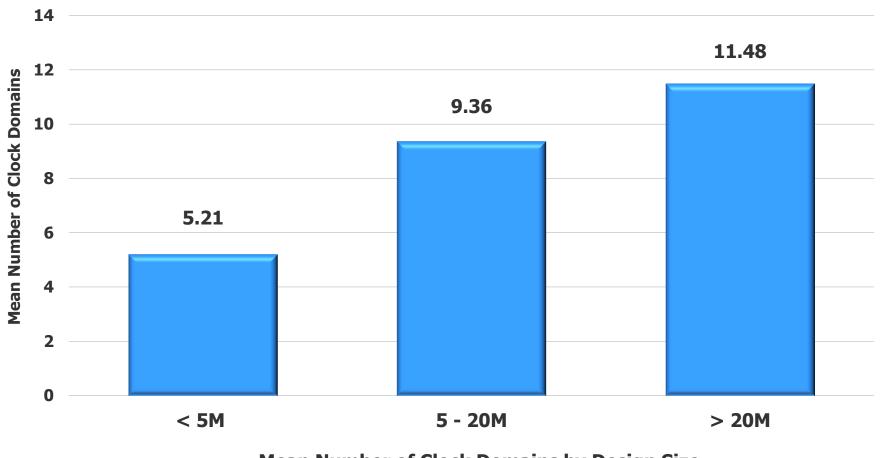

- Verify multiple clock domain crossings

## Mean Number of Clock Domains by Design Size

### Mean Number of Clock Domains by Design Size (Gates Excluding Memories)

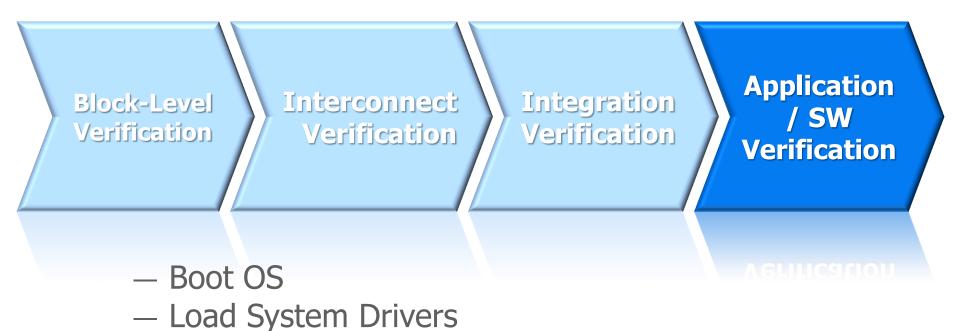

## **Standardization of the SoC Verification Process**

– Run Application SW

## SoC Design & Verification Involves Lots of SW

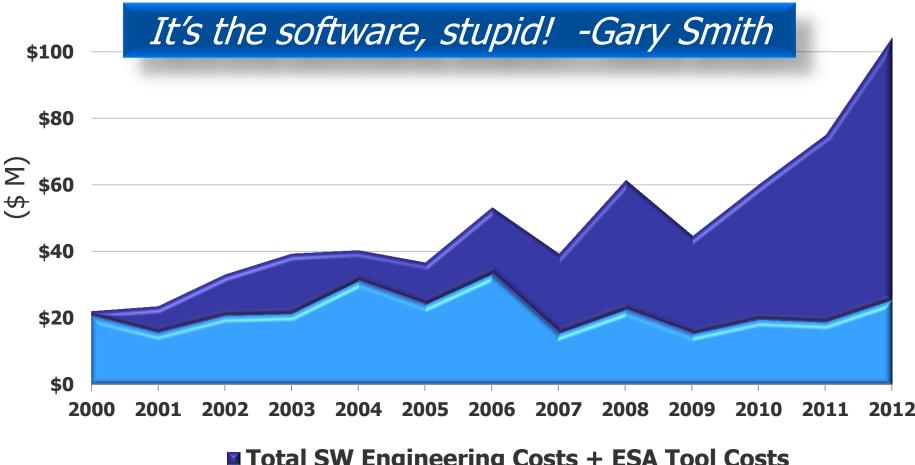

# Total SW Engineering Costs + ESA Tool Costs Total HW Engineering Costs + EDA Tool Costs

Source: ITRS 2010, Impact of Design Technology on SoC Consumer Portable Implementation Cost

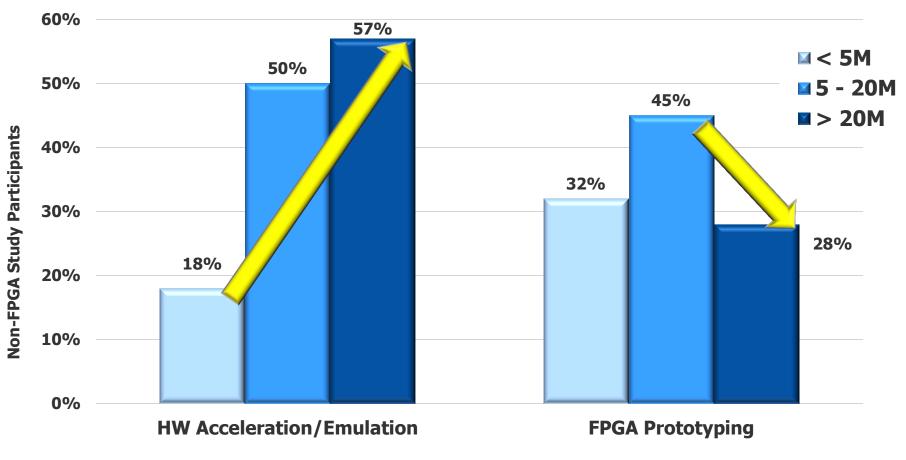

## As Design Sizes Increase...Emulation Up, FPGA Prototyping Down in 2012

### Adoption by design size for those doing HW acceleration/emulation and FPGA Prototyping

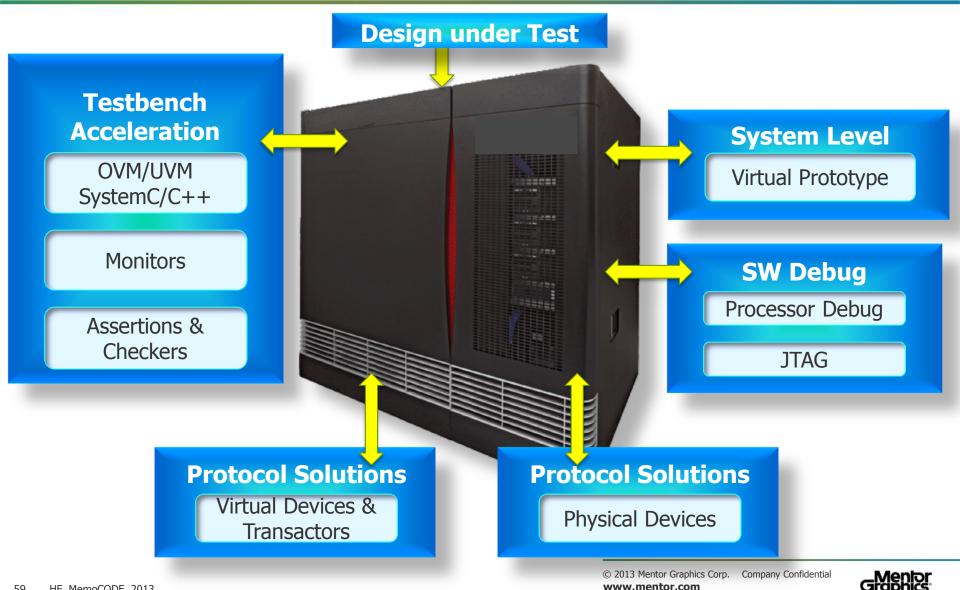

## **Integrated Simulation/Emulation/Software Verification Environments Emerge**

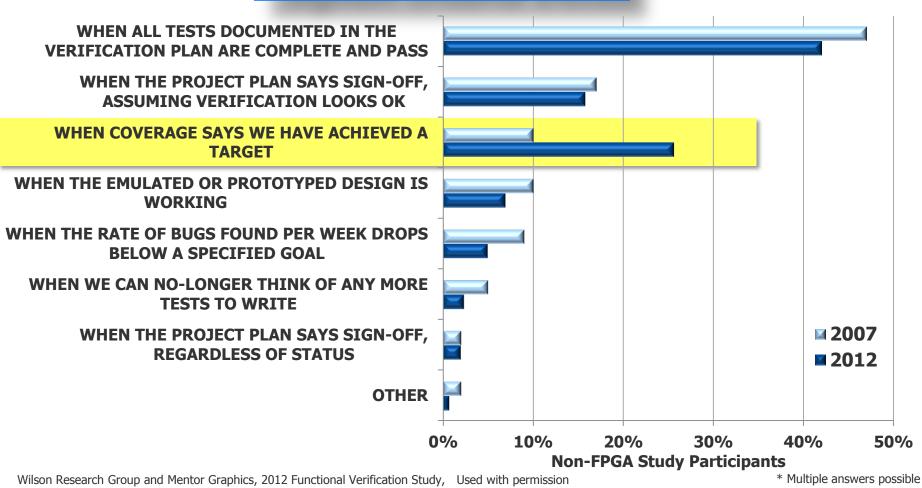

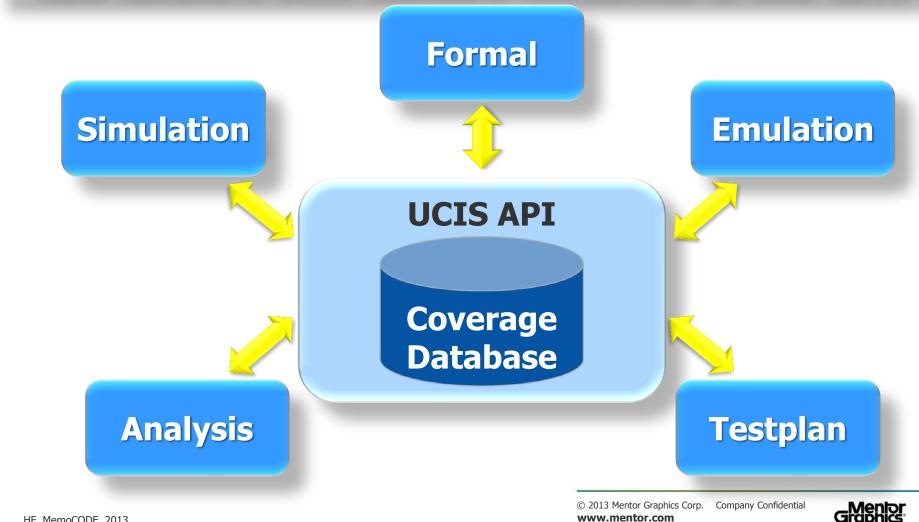

## **Coverage and Power**

Across all aspects of verification

# **The Rising Importance of Coverage**

### **Unified Coverage Interoperability Standard**

New Accellera UCIS Standard Announced at DAC 2012

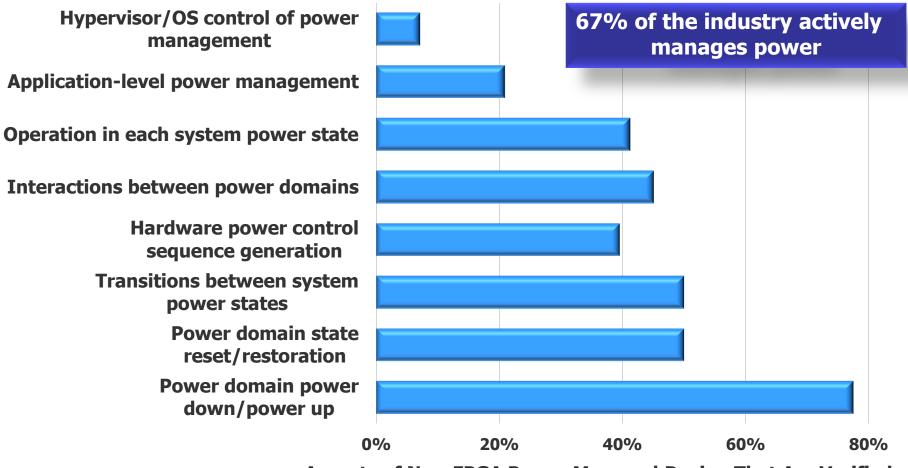

# **Trends in Power Management Verification**

Aspects of Non-FPGA Power Managed Design That Are Verified

Source: Wilson Research Group and Mentor Graphics, 2012 Functional Verification Study, Used with permission

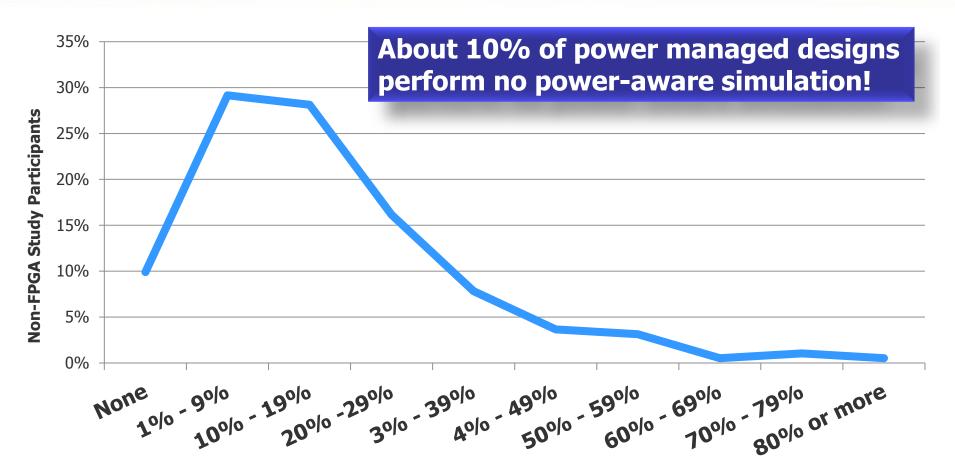

# **Power Trends**

### Percentage of total simulations that were power-aware

Wilson Research Group and Mentor Graphics, 2012 Functional Verification Study, Used with permission

HF - January 2013 Master Set, WRG & MG Study Results

# **Power Trends**

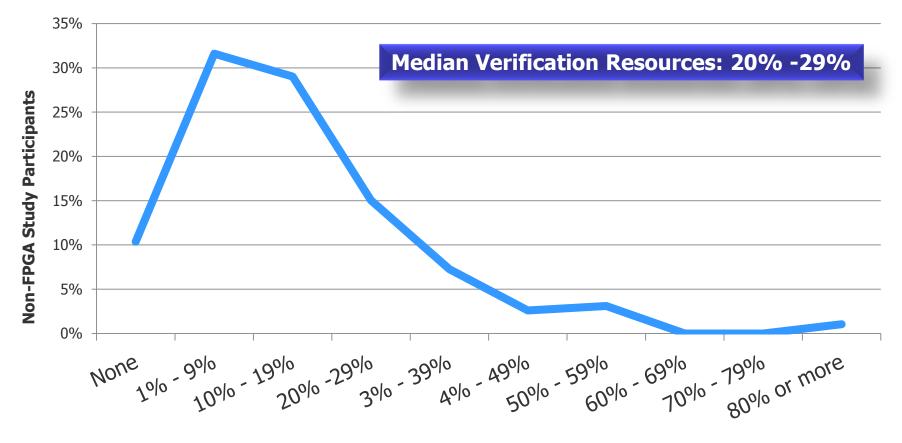

### Percentate of Verification Resources Focused on Power Management

Wilson Research Group and Mentor Graphics, 2012 Functional Verification Study, Used with permission

# **Power Trends**

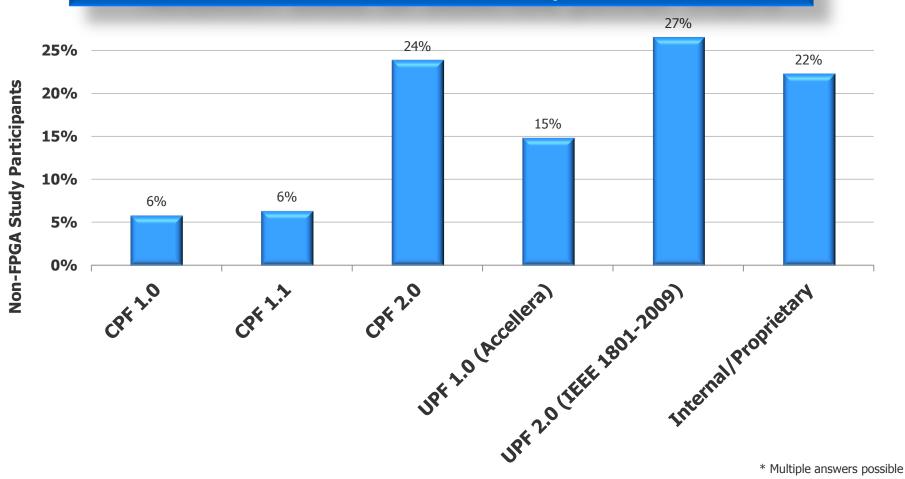

Notation used to describe power intent

Source: Wilson Research Group and Mentor Graphics, 2012 Functional Verification Study, Used with permission

© 2013 Mentor Graphics Corp. Company Confidential **www.mentor.com**

## **Beyond the Status Quo**

Standardization of the SoC Verification Process

The Productivity Gap

# **BACK TO THE FUTURE**

HFB MemoCODE, 2013

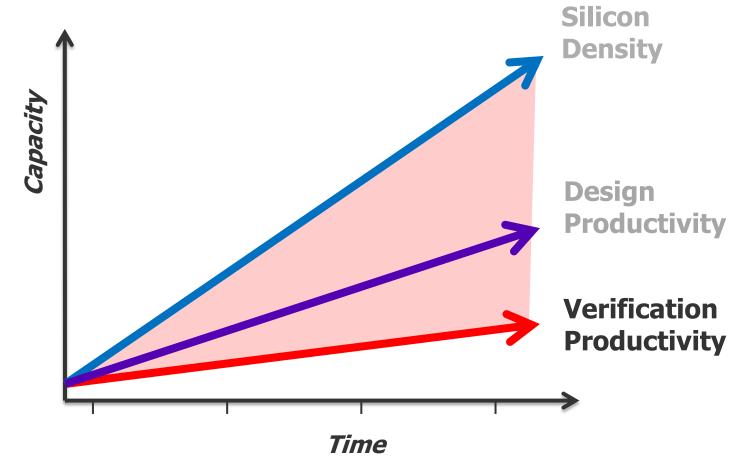

# **Design Productivity Gap**

# **Verification Productivity Gap**

Source: SEMATECH

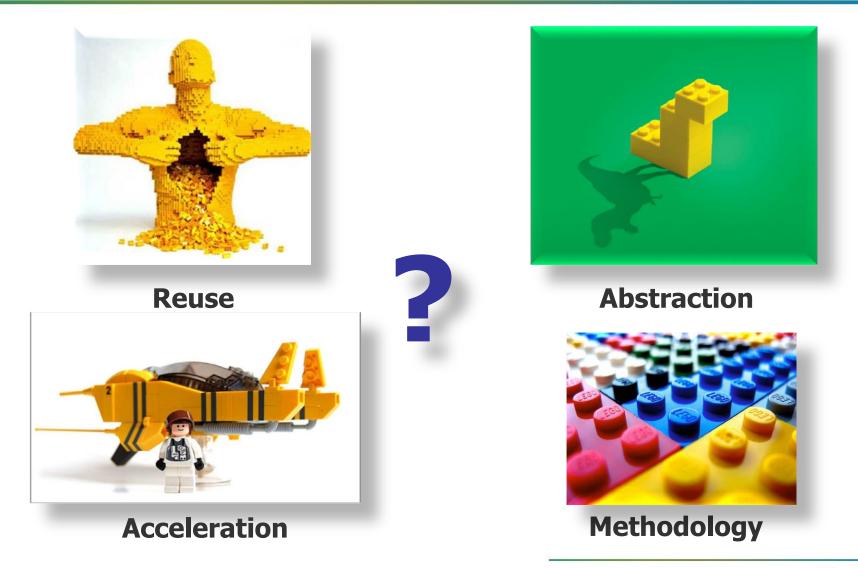

# **Closing The Verification Gap**

# **Managing Complexity**

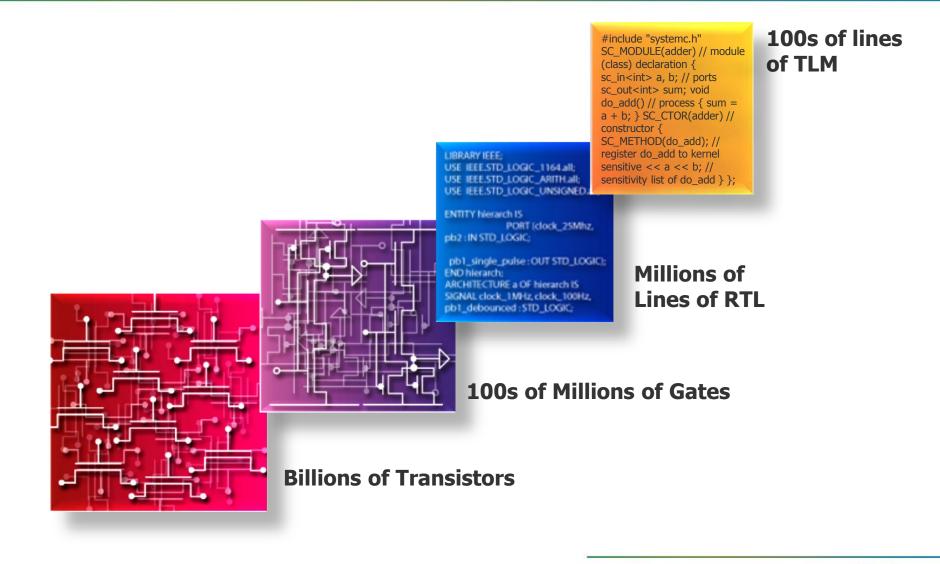

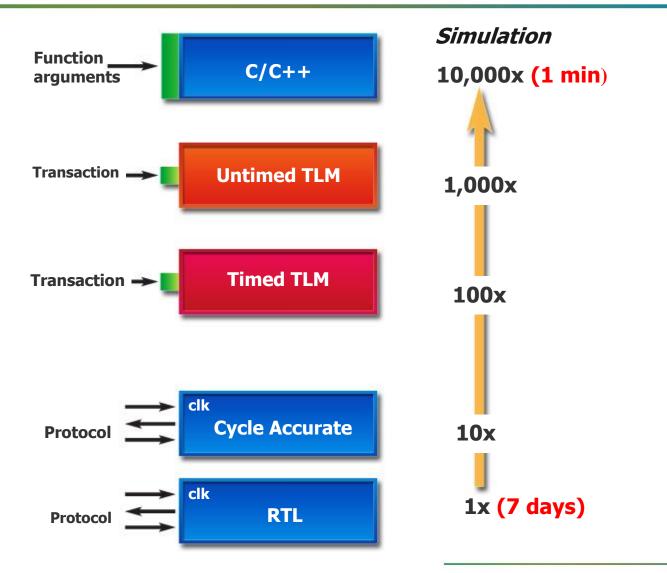

# **Productivity Gains Through Abstraction**

# **Bug Prevention vs. Bug Hunting**

What's the advantage of SystemC compared with RTL?

There are two different aspects – quality and time schedule. Today, a full chip on SystemC will run around 10 MHz, and you will never reach that speed using RTL or a lower-level abstraction. It's similar to a prototype speedup. Previously with RTL designs, our bug rate was in the range of 10 to 50 bugs per square millimeter. Now we are at less than one bug per millimeter squared. So we have both quality and speed of development.

Source: EETimes, 2007, Laurent Ducousso, who manages intellectual-property (IP) verification for STMicroelectronics' Home Entertainment Division

# Summary

- Beyond theory in terms of rising complexity

- Beyond arguing over who won the standards wars

- Beyond surviving by maintaining the status quo

www.mentor.com