Day 1 (FRIDAY, October 18)

8:00 Breakfast

and Registration

8:45 Welcome

(slides)

9:00 1st

Session 1: Prototyping Part I

chair: Arvind, MIT

·

Matthew Anderson and Sandeep Shukla

APECS: An

AADL and Polychrony Based Embedded Computing System Design Environment and

an Elevator

Case Study (slides)

·

Thomas Kuhn,

Thomas Forster, Tobias Braun, and Reinhard Gotzhein

FERAL –

Framework for Simulator Coupling on Requirements and Architecture Level (slides)

· Katell Morin-Allory, Fatemeh Negin Javaheri, and Dominique Borrione

Fast Prototyping from Assertions: a Pragmatic Approach (slides)

10:30 Coffee Break

11:00 1st Keynote – chair: Ivan Sutherland, Portland State University

· Guest Appearance:

Tad McGeer, Aerovel (slides)

· Keynote: Lee Pike, Galois

Building

a High-Assurance Unpiloted Air Vehicle (slides)

12:30 Lunch

14:00 2nd Session: Dataflow and

Communication Fabrics

chair: Jean-Pierre Talpin, INRIA

·

Robert de Groote, Philip

Hölzenspies, Jan Kuper, and Hajo Broersma

Back to Basics: Homogeneous Representations of Synchronous

Dataflow Graphs (slides)

·

Firew Siyoum, Marc Geilen,

Johan Eker, Carl von Platen, and Henk Corporaal

Automated Extraction of Scenario Sequences from Disciplined

Dataflow Networks (slides)

·

Sebastiaan

Joosten

and Julien Schmaltz

Generation of

Inductive Invariants from Register Transfer Level Designs of Communication

Fabrics (slides)

·

Sayak Ray

and Robert Brayton

Ranking

Structure in Communication Fabrics (slides)

16:00 Coffee Break

16:30 2nd

Keynote – chair: Fei Xie, Portland State

University

·

Yatin Hoskote, Intel

Designing

Tomorrow's Chips (slides)

18:00 Banquet & International

Exhibition of Sherlock Holmes

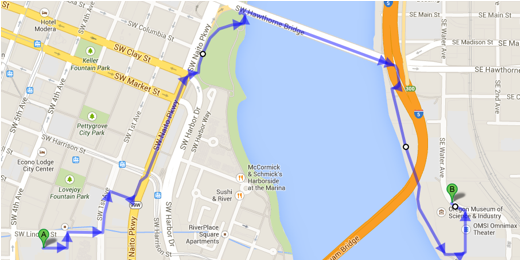

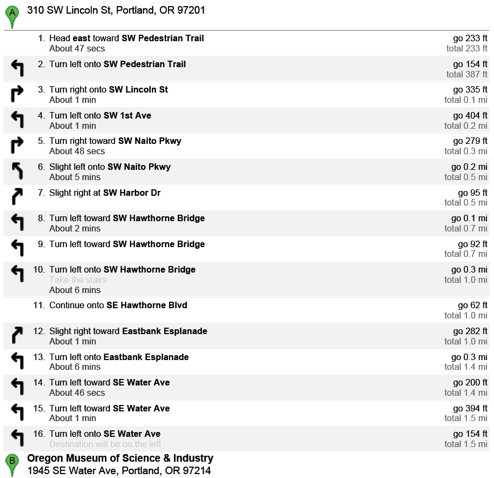

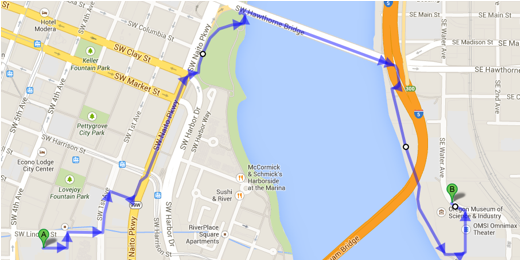

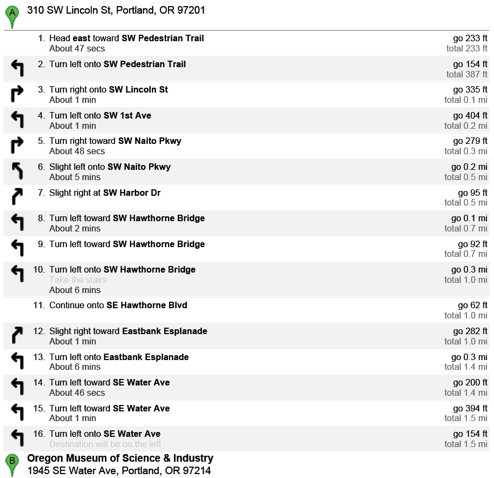

Oregon Museum

of Science and Industry (OMSI), 1945 SE Water Ave, Portland, OR 97214

Day 2 (SATURDAY, October 19)

8:10 3rd

Session: Probabilistic Systems

chair: Marly Roncken, Portland

State University

· (20 min. video-skype session with the University of

M'sila, Algeria)

Hichem Debbi and Mustapha Bourahla

Causal

Analysis of Probabilistic Counterexamples (slides)

· Saddek Bensalem, Axel Legay, Ayoub Nouri, and Doron Peled (slides)

Synthesizing Distributed Scheduling Implementation for

Probabilistic Component-based Systems

9:00 4th

Session: SW and HW Model Validation

chair: Rajesh Gupta, UCSD

·

Cynthia Sturton, Rohit Sinha, Thurston Dang, Sakshi

Jain, Michael McCoyd, Wei Yang Tan,

Petros Maniatis, Sanjit Seshia, and David Wagner

Symbolic

Software Model Validation (slides)

·

Vidura Wijayasekara and Sudarshan Srinivasan

Equivalence

Checking For Synchronous Elastic Circuits (slides)

·

Carlos Villarraga, Bernard Schmidt, Jörg Bormann, Christian Bartsch, Dominik Stoffel, Wolfgang

Kunz

An

Equivalence Checker for Hardware-Dependent Embedded System Software (slides)

10:30 Coffee

Break

11:00 3rd

Keynote – chair: Ren Su, Dean Maseeh

College, Portland State University

·

Harry Foster,

Mentor Graphics

Industry

Pulse: Trends in Function Verification (ppt) (pdf)

12:30 Lunch

14:00 Design Contest – chair: Eriko Nurvitadhi, Intel

·

Eriko Nurvitadhi

MEMOCODE 2013

Hardware/Software Co-design Contest: Stereo Matching (slides)

· Armin Ahmadzadeh, Hatef

Madani, Kianoush Jafari, Farzad Salimi

Jazi, Shervin Daneshpajouh, and Saeid Gorgin

Fast and

Adaptive BP-based Multi-core Implementation for Stereo Matching (slides)

· Jungwook Choi and Rob Rutenbar

FPGA

acceleration of Markov Random Field TRW-S Inference for Stereo Matching (slides)

·

Hassan Eslami, Theodoros Kasampalis, and Maria Kotsifakou

A GPU

Implementation of Tiled Belief Propagation on Markov Random Fields (slides)

Award

Ceremony (photo)

·

Certificates and

cash prize awards sponsored by Intel and Mentor Graphics,

handed

over by Eriko Nurvitadhi (on behalf of Yatin Hoskote) and by Harry Foster

·

Photographer:

Hoon Park, Portland State University

15:30 Coffee Break

16:00 5th Session: Prototyping

Part II

chair: Yi Deng, Virginia Tech

·

Florin Balasa,

Ilie Luican, Noha Abuaesh, and Cristian Gingu

Compiler-Directed

Memory Hierarchy Design for Low-Energy Embedded Systems (slides)

·

Frederic Mallet, Jean-Vivien Millo, and Robert de Simone

Safe CCSL Specifications

and Marked Graphs (slides)

·

Manuel Gesell and Klaus

Schneider

Translating Synchronous Guarded Actions to Interleaved

Guarded Actions (slides)

·

Muralidaran

Vijayaraghavan, Nirav Dave, and Arvind

Modular Compilation of Guarded Atomic Actions (slides)

18:00 Closing Remarks (slides)

Day 3 (SUNDAY, October 20)

Tutorial Day

chair: Malay Ganai, NEC Laboratories

America

08:00 Breakfast

and Registration

08:50 Welcome

(slides)

09:00 1st

Tutorial

Rajeev Alur, University of Pennsylvania

Syntax-Guided

Synthesis (slides)

10:30 Coffee

Break

11:00 2nd

Tutorial

Nate Foster, Cornell University

Arjun Guha, University of Massachusetts Amherst

Mark Reitblatt, Cornell University

Cole Schlesinger, Princeton University

Network

Programming in Frenetic (slides)

12:30 Lunch

14:00 3rd

Tutorial

Jim Grundy, Intel Corporation

Firmware

Validation: Challenges and Opportunities (slides)

15:30 Coffee

break

16:00 4th

Tutorial

Somesh Jha, University of Wisconsin, Madison

Tom Reps, University of Wisconsin, Madison

Bill Harris, University of Wisconsin, Madison

Secure

Programs via Game-based Synthesis (slides)

18:00 FMCAD Reception

University

Place Hotel, Willamette Room